SXoM

System-on-Module Solutions by Solectrix

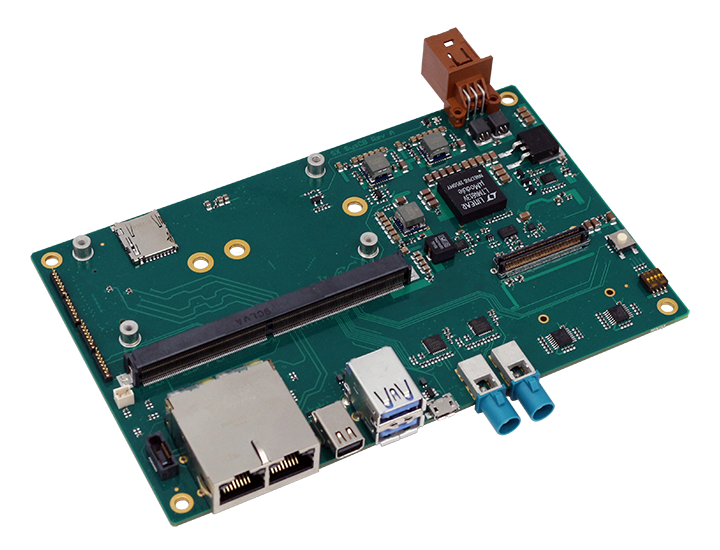

System-on-Modules are the state-of-the-art solution for applications in highly technologized areas such as medical technology, the automotive industry, industrial automation, aerospace and others. Their modular approach allows for a high degree of customization on the application hardware side with the broad support for established industry standards like COM Express® SMARC™ offering a wide choice of standardized system cores compliant with the respective SoM format. The need for ultra-compact modules that combine CPU and FPGA led to the launch of the SXoM series, a line of System-on-Module boards by Solectrix.

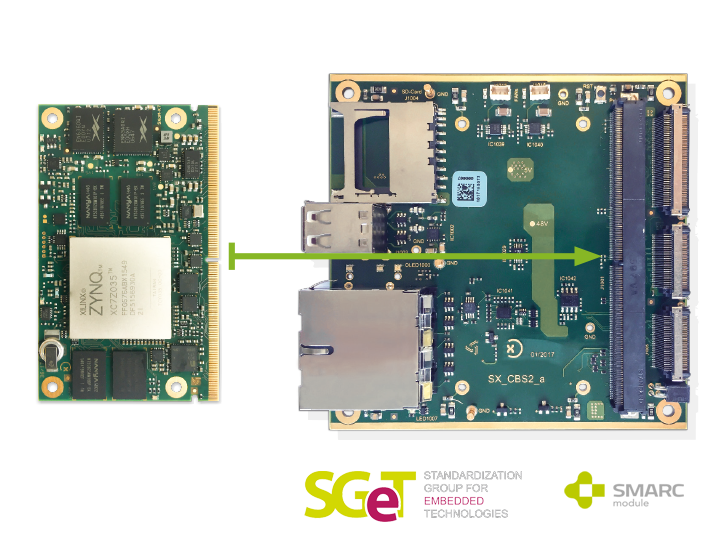

Solectrix is a member of SGET, the Standardization Group for Embedded Technologies, and supports the SMARC™ 2.0 standard with System-on-Modules and matching carrier boards.

For more information on the SMARC™ specification please visit: www.sget.org

The following types of SXoM boards are available:

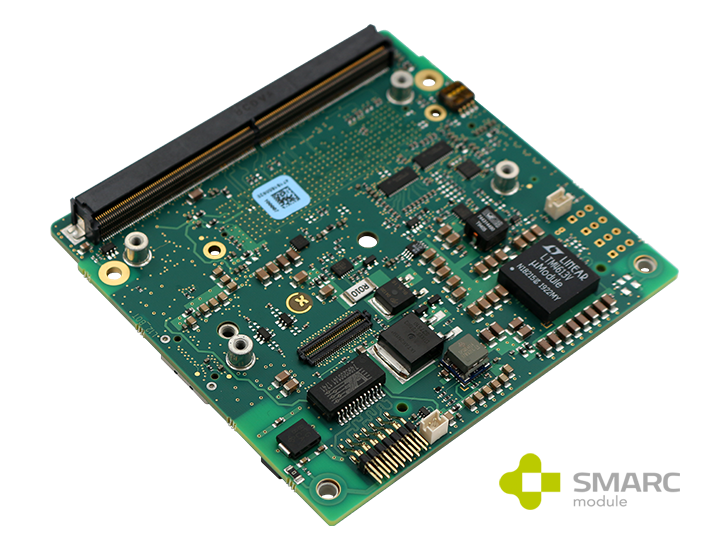

COM Express® system-on-modules:

- SXoM ME-ZU with AMD Zynq™ UltraScale+™ ZU11/17/19EG MPSoC

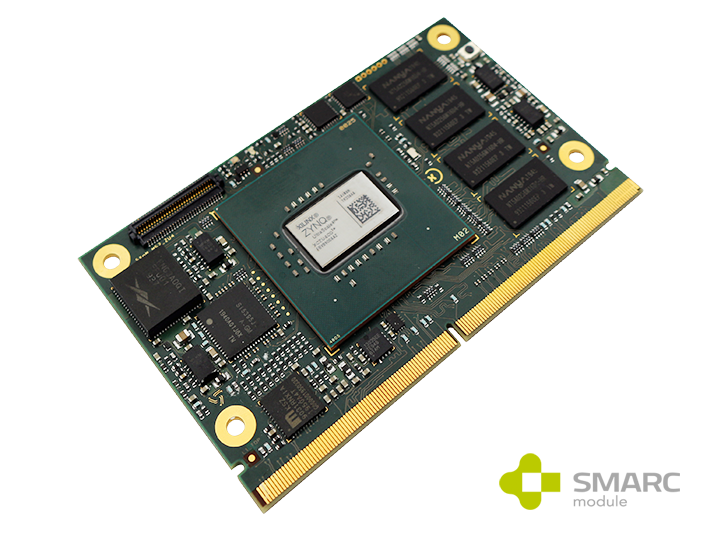

SMARC™ system-on-modules:

- SXoM MS2-ZU with AMD Zynq™ UltraScale+™ ZU4/5/7 MPSoC

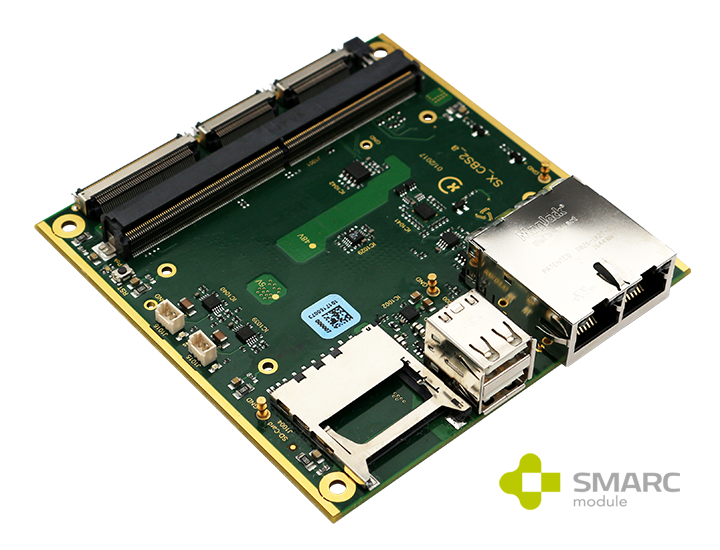

SMARC™ carrier boards: